2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

FPGA冬令营每日一讲:郑同学分享串口控制FLASH读写

FPGA冬令营每日一讲:郑同学分享串口控制FLASH读写

冬日逐光,笃行致远。成电国芯FPGA冬令营在成都AI创新中心持续开展,“每日一讲”环节作为实战教学的重要延伸,始终坚持让学员站上讲台、分享所学、碰撞思路。近日,郑同学以《串口控制FPGA读写》为题,结合自身实操经验与技术沉淀,为全体营员带来了一场兼具理论深度与实战价值的技术分享,用干货满满的内容点亮冬日学习时光。

串口通信作为FPGA开发中跨设备数据交互的核心技术,是连接上位机与FPGA开发板的重要桥梁,广泛应用于嵌入式系统、工业控制、智能硬件等多个领域。郑同学开篇即点明串口控制FPGA读写的实用价值,结合冬令营实操训练中常用的Xilinx开发平台,从技术原理、模块设计、实操验证三个维度展开分享,层层递进、逻辑清晰。

在技术原理讲解环节,郑同学聚焦UART串口通信协议核心,用通俗的语言拆解了异步收发的底层逻辑,重点阐述了起始位侦测、数据位采样、校验位配置与停止位识别的完整流程。他特别提到,为提升通信稳定性,实际开发中可采用多倍频采样技术,通过16倍波特率时钟对数据位进行多次采样,有效规避信号干扰带来的误码问题,这一细节分享精准贴合了冬令营项目实战中的常见痛点。

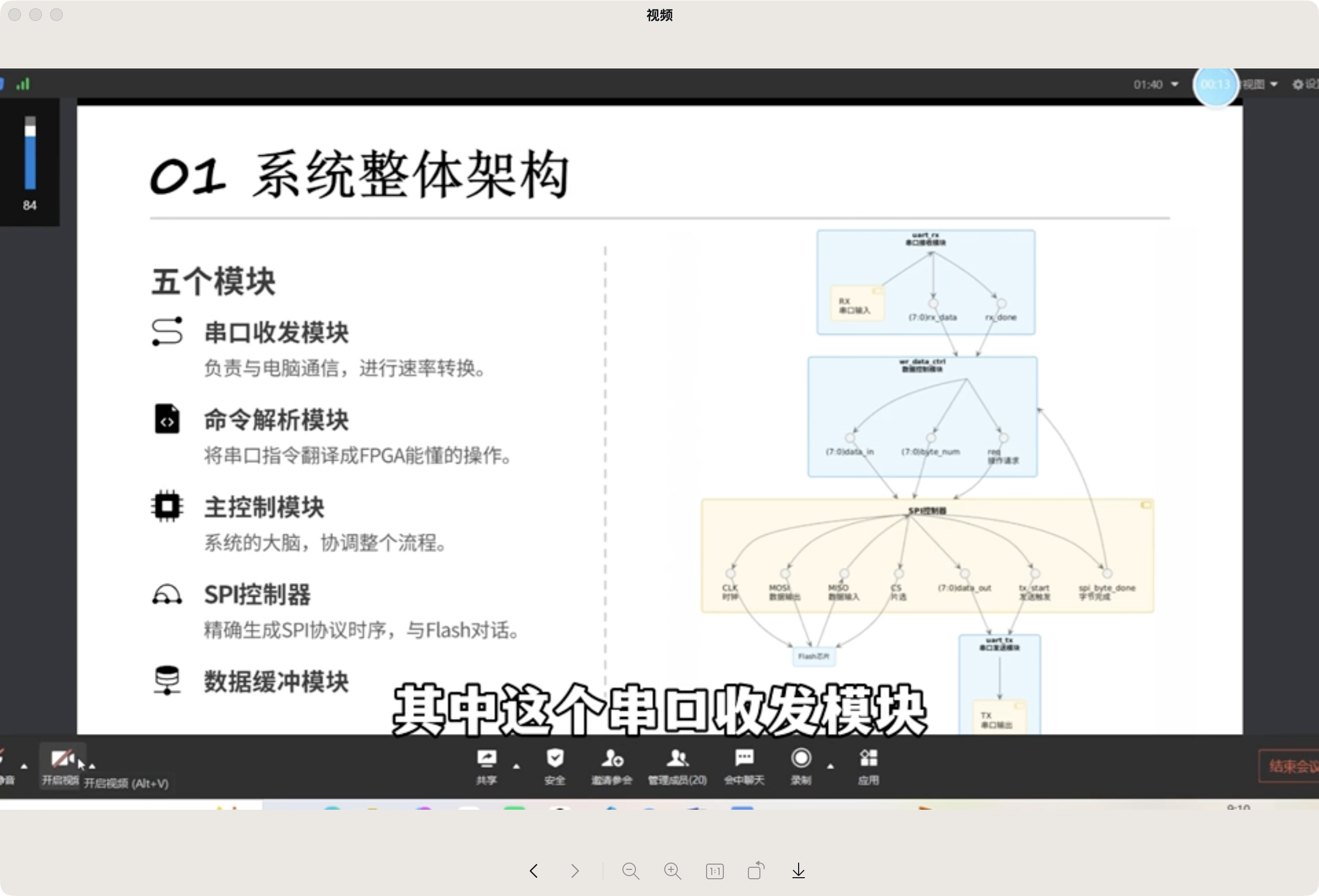

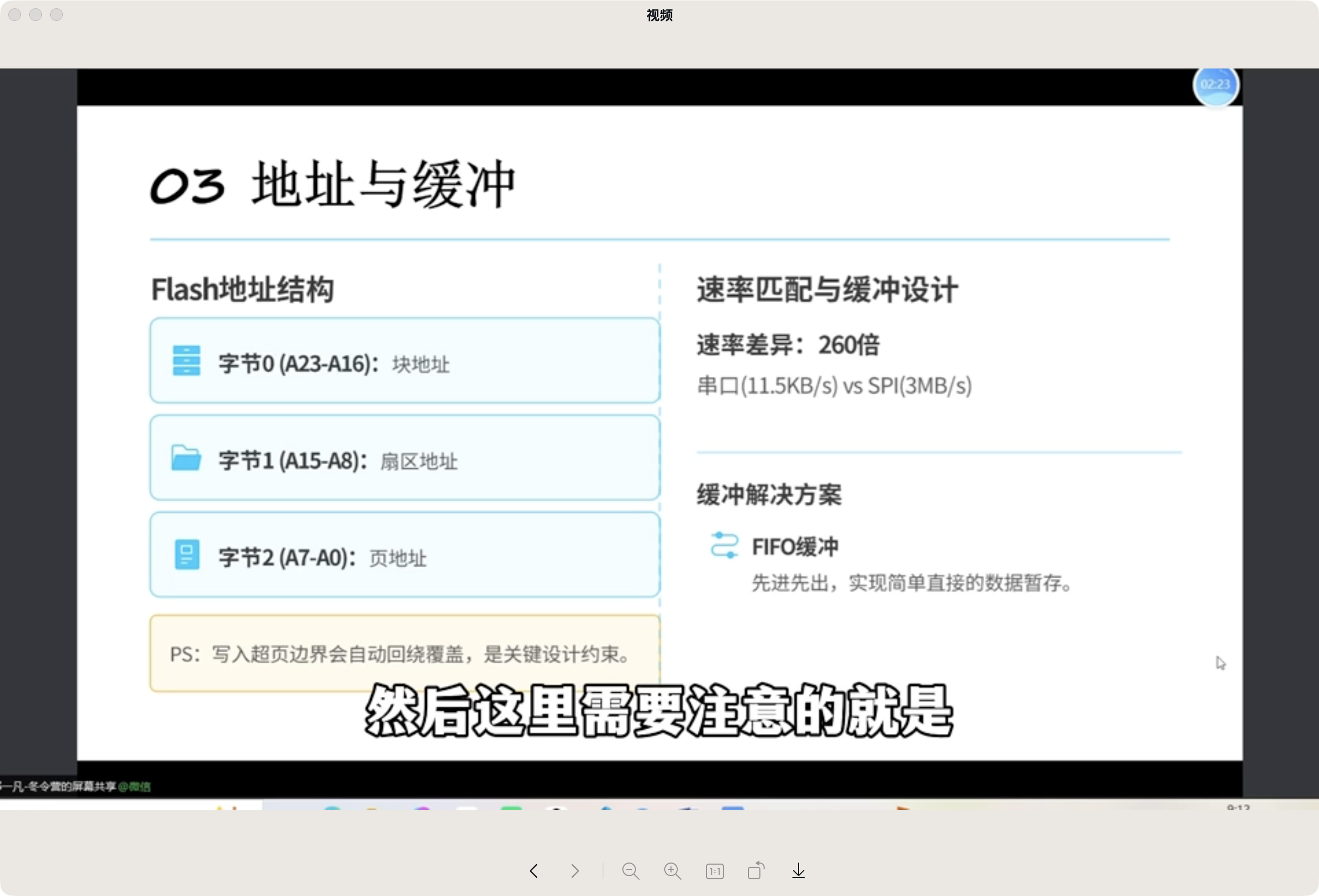

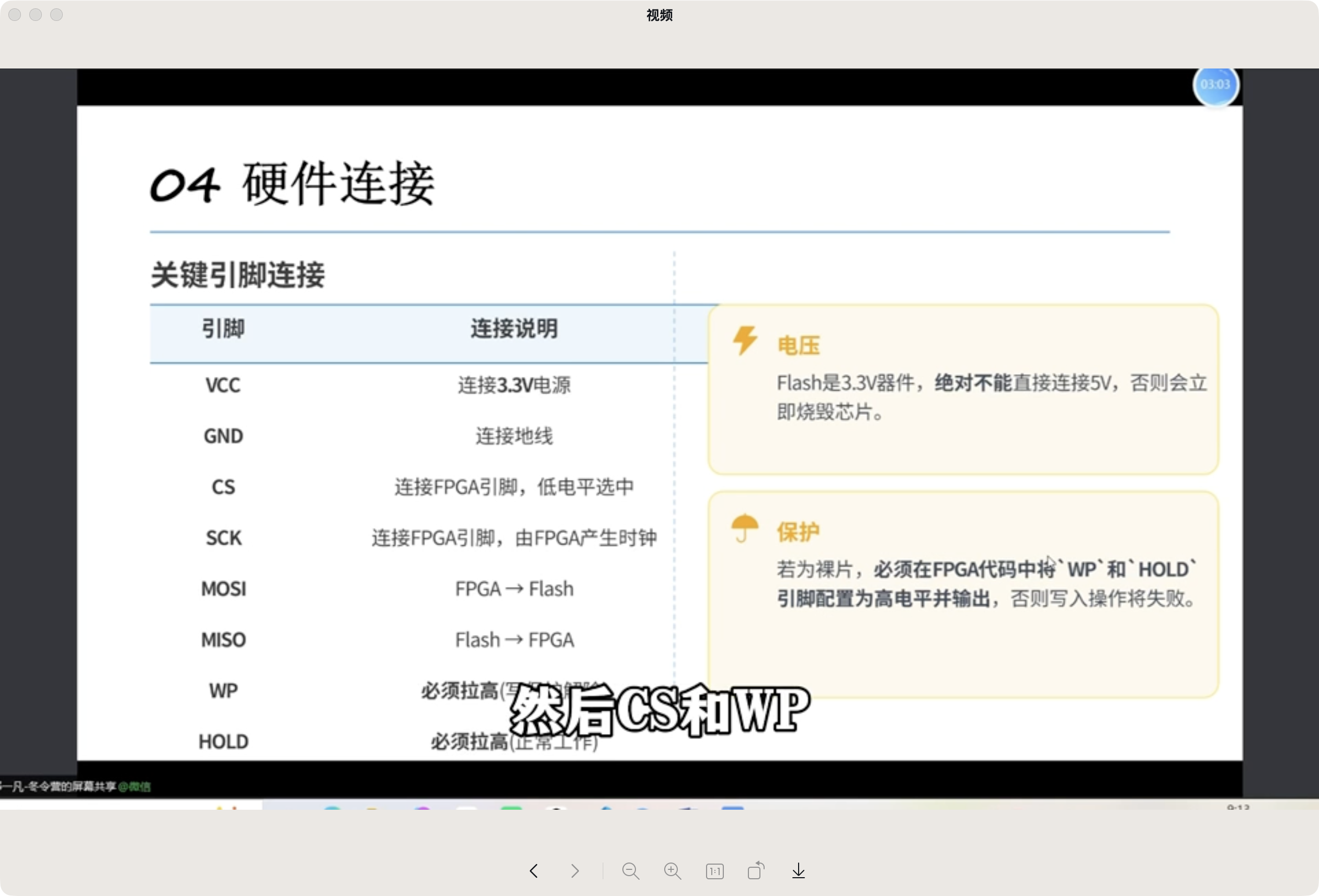

模块设计部分,郑同学结合Verilog HDL编程实战,详解了串口控制FPGA读写的模块化架构设计。他以顶层模块`uart_op.v`为核心,依次介绍了数据收发模块`data_tx_rx.v`与控制模块`UART_Ctrl.v`的功能分工与接口联动逻辑——数据收发模块承担缓冲区管理与数据调度职责,通过FIFO结构实现并行数据与串行数据的转换适配;控制模块则负责波特率配置、中断生成与读写使能控制,二者协同构建起稳定可靠的数据通路。同时,他还分享了参数化设计技巧,通过灵活调整时钟频率与波特率参数,实现同一套代码在不同硬件平台的适配复用,展现了扎实的工程设计思维。

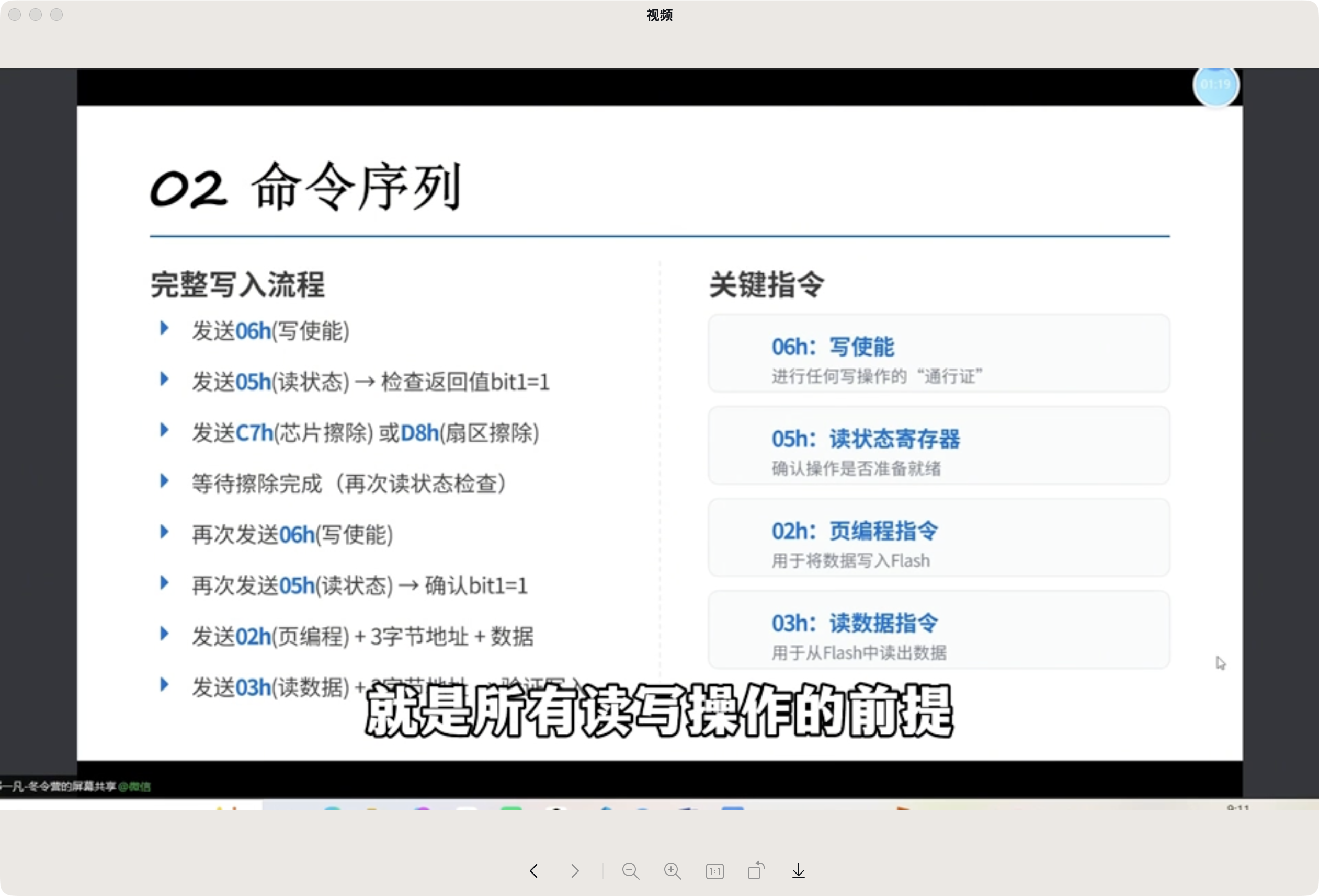

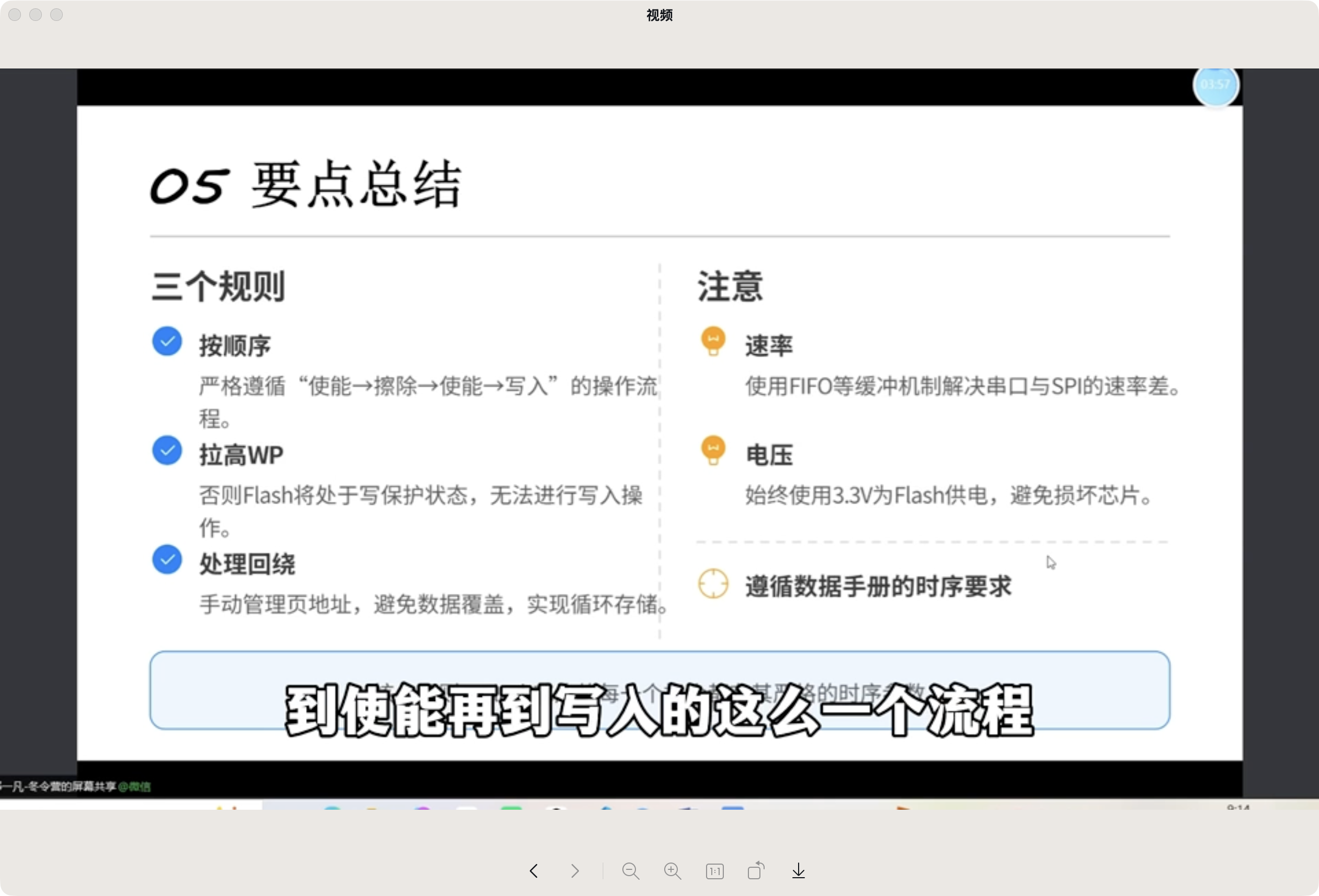

实战验证环节是本次分享的亮点。郑同学结合冬令营实操案例,现场复盘了上板测试的完整流程:从Verilog代码编写与综合,到开发板与上位机的串口连接配置,再到数据写入、读取与一致性验证,每一步都附带实操要点与排错技巧。他提到,在初期调试中曾遇到数据丢失问题,最终通过优化缓冲区设计、调整时钟分频系数得以解决,这种“问题导向”的分享方式,让在场营员深受启发,纷纷结合自身实操中遇到的问题展开提问。

分享互动环节气氛热烈,营员们围绕“串口速率自适应优化”“多设备串口通信冲突解决”“FPGA与DDR内存的串口联动读写”等问题与郑同学深入探讨。郑同学结合搜索到的自适应串口读写设计思路,分享了协议转换与寄存器控制的优化方案,现场导师也针对工业场景中的实际应用需求,补充了高速串口通信的进阶技巧,进一步拓宽了营员的技术视野。

成电国芯FPGA冬令营始终秉持“理论筑基、实战赋能”的教学理念,通过“每日一讲”“项目攻坚”等多元化环节,让学员在输出与交流中深化技术理解,培养“技术+表达”的复合型能力。正如郑同学在分享结尾所说,串口控制技术是FPGA开发的“入门钥匙”,唯有扎实掌握基础模块设计,才能在复杂项目中灵活应用、突破创新。

接下来,成电国芯FPGA冬令营将继续聚焦硬核技术教学,持续为营员搭建交流分享的优质平台,助力学员在沉浸式实战中实现技术跃迁,为IC领域培育更多兼具理论功底与工程能力的优质人才。