2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

成电国芯FPGA就业班中期项目考核答辩圆满落幕:以实战锤炼技术,以能力实现高薪

成电国芯FPGA就业班中期项目考核答辩圆满落幕:以实战锤炼技术,以能力实现高薪

2025年5月18日,成电国芯FPGA就业班迎来中期项目考核答辩。本次考核聚焦学员对FPGA开发技术的综合应用能力,通过项目开发、成果展示与现场答辩等环节,全方位检验学员的技术水平与实践能力,为后续的进阶学习与就业打下坚实基础。

项目亮点纷呈:多维技术能力全面展现(筛选3个)

本次中期考核涌现出一批高质量项目,充分展现了学员在图像处理、系统设计与算法优化等领域的扎实功底:

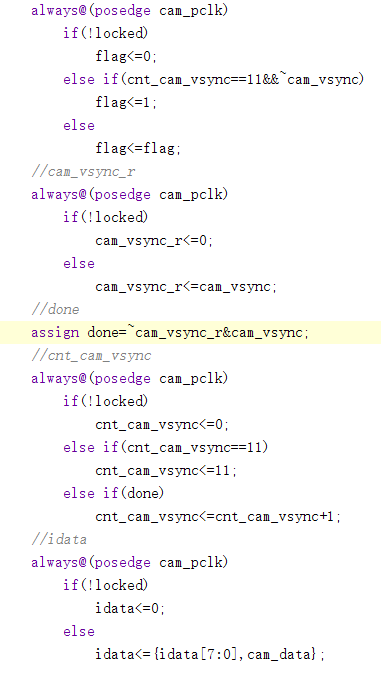

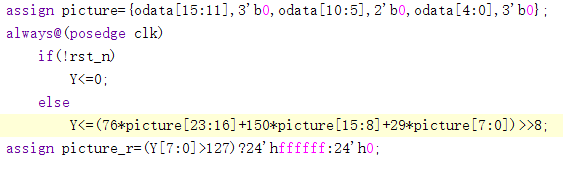

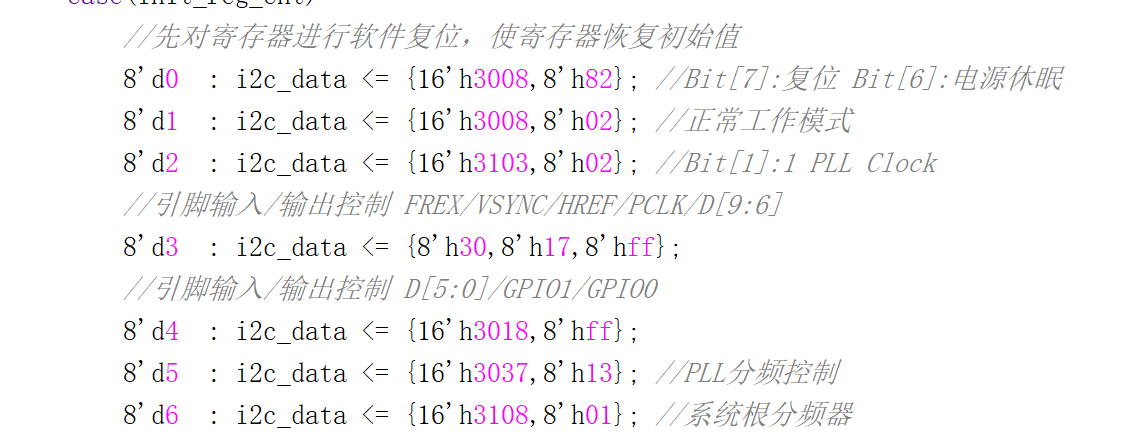

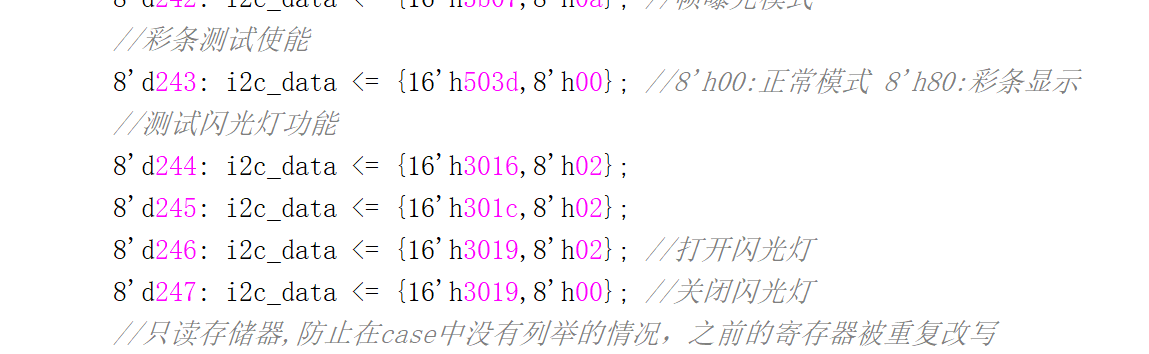

基于OV5640的图像采集与实时显示系统

学员通过FPGA驱动OV5640摄像头模块,实现了高帧率图像采集与实时显示,重点攻克了硬件接口时序控制、图像数据缓存优化等核心问题,展现了硬件系统设计能力。

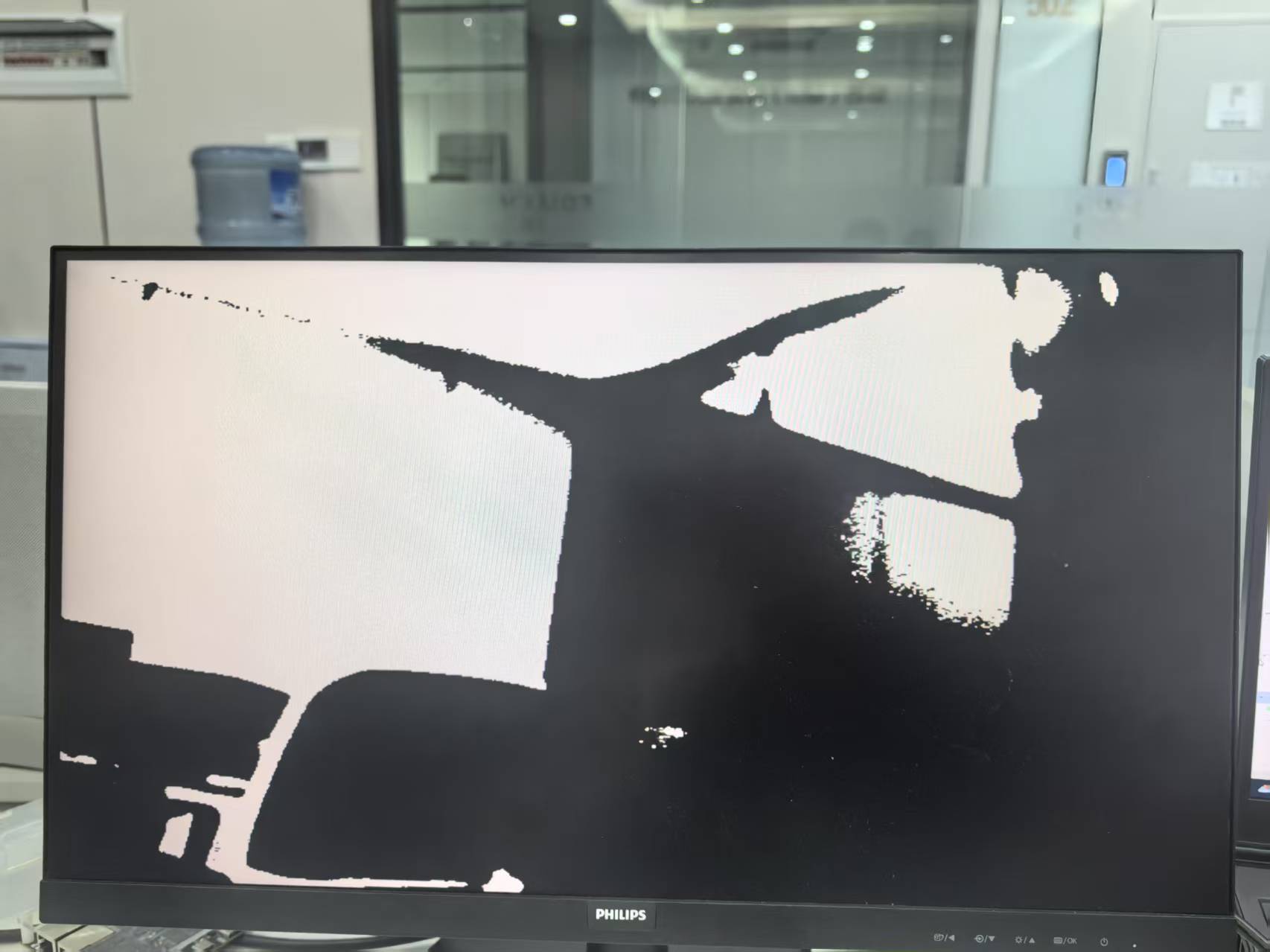

FPGA图像传输与边缘检测算法实现

结合千兆以太网或HDMI接口,学员完成了图像数据的稳定传输,并基于Sobel算子实现了实时边缘检测,在资源占用与算法效率之间取得平衡,体现了软硬件协同优化能力。

FPGA平台简易贪吃蛇游戏开发

通过VGA显示模块与按键交互,学员独立完成贪吃蛇游戏的逻辑设计、碰撞检测与动态显示,项目融合了状态机设计、外设控制与实时性处理,凸显了FPGA在嵌入式系统开发中的灵活性。

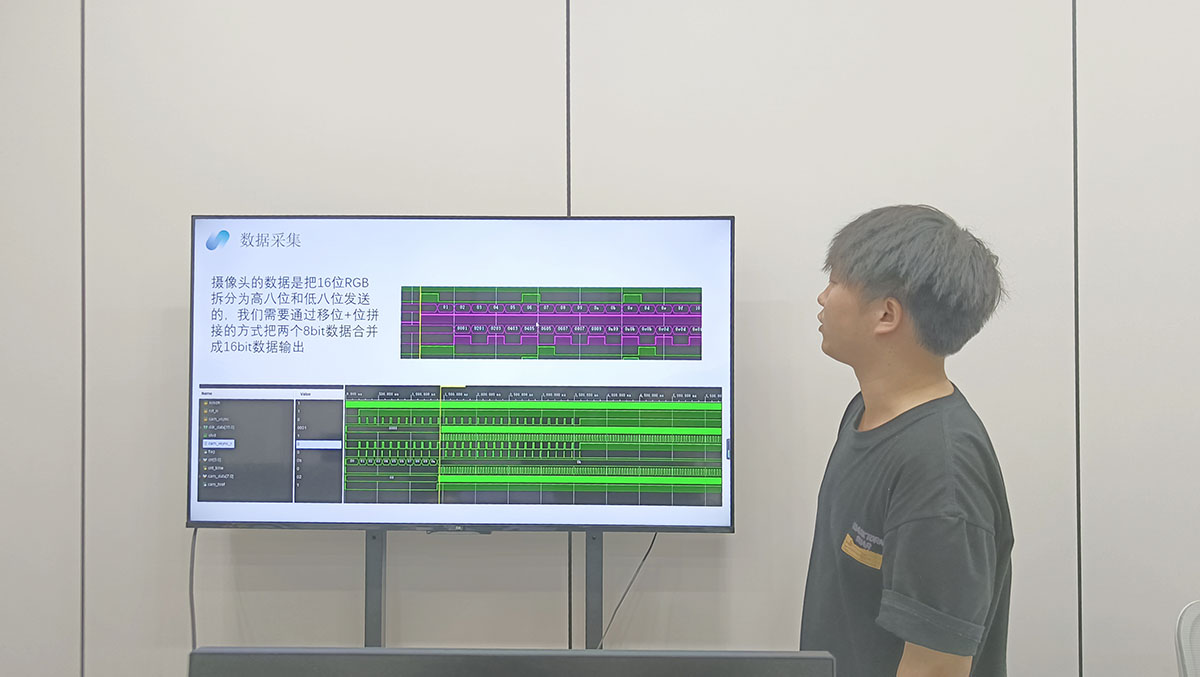

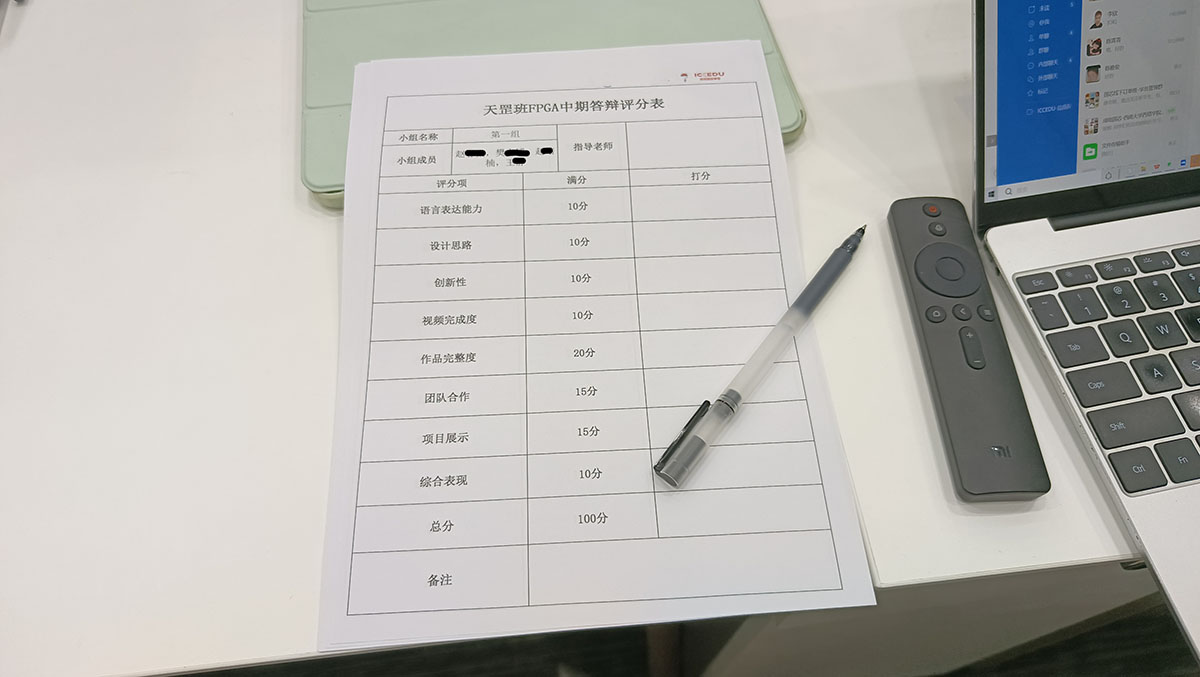

答辩现场回顾:严谨评审助力成长

答辩环节中,学员通过PPT讲解、代码演示与功能实测,系统阐述项目设计思路与技术难点。成电国芯技术导师团队从功能完整性、代码规范性、创新性、答辩逻辑性四个维度进行严格评审,并提出针对性优化建议,例如:

- 图像传输项目的抗干扰设计改进方案

- 边缘检测算法的多级流水线优化策略

- 贪吃蛇游戏随机生成机制的扩展方向

导师组强调:“中期考核不仅是技术能力的检验,更是培养学员工程化思维、文档撰写与沟通表达能力的关键环节。只有通过高标准、实战化的项目打磨,才能为行业输送真正合格的FPGA工程师。”

学员感言:从理论到实战的蜕变

“通过这次项目实战,我对FPGA的并行处理优势有了更深刻的理解。导师的严格要求和项目复盘让我意识到,代码优化和文档规范与功能实现同样重要。”——学员王同学

“贪吃蛇项目从零开始调试时遇到了很多问题,但解决问题的过程让我真正掌握了状态机设计和时序分析的方法。”——学员赵同学

结语:以技术为本,以严格护航未来

成电国芯FPGA培训始终秉持“技术立身、实战为先”的理念,通过分阶段项目考核体系,确保学员逐步掌握从基础到进阶的核心技能。中期答辩的圆满成功,标志着学员已具备独立开发FPGA中小型系统的能力,也为后续的复杂项目开发与就业冲刺奠定了坚实基础。

加入成电国芯,让技术梦想在FPGA的世界里加速起航!

(成电国芯FPGA成都培训基地 供稿)