2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

程序员转行FPGA的心理与技术障碍分析

程序员转行FPGA的心理与技术障碍分析

一、职业安全感与风险规避心理分析

1.1 职业安全感缺失的心理机制

程序员职业安全感的缺失源于多重不确定性的叠加,这种心理状态在心理学中可被归为“安全感缺失综合征”的典型表现。软件行业的技术迭代速度与项目周期压缩特性,持续冲击着从业者对“职业稳定性”的基本心理需求。网络泡沫时期IT业大规模裁员的历史事件,形成了行业集体记忆中的“失业恐惧”烙印,这种记忆会通过职场前辈的经验传递、行业周期波动的反复验证而不断强化。当程序员观察到身边同事因技术栈过时被优化,或听闻某热门框架在半年内被新工具取代时,会本能地将这种外部变化内化为对自身技能有效性的怀疑,进而产生“无序恐惧”——即担心现有知识体系在短时间内失效,而新的技术标准尚未完全掌握。

传统文化中的“秩序情结”进一步加剧了这种焦虑。多数程序员成长过程中接受的教育强调“循序渐进”“一分耕耘一分收获”的线性成功路径,但软件行业的发展规律却呈现非线性特征:某编程语言可能在一年内从“必学技能”沦为“ legacy 技术”,某项目经验可能因公司战略调整瞬间失去价值。这种现实与心理预期的冲突,使得从业者在面对技术选择时更容易陷入“路径锁定”——既不敢完全放弃已有技能体系,又难以确定新方向的投入是否能形成稳定回报,最终在“求稳”与“求变”的矛盾中消耗心理资源。

职业安全感的缺失还体现在对“不可替代性”的误判上。部分程序员通过掌握项目核心逻辑、保留关键实现细节等方式构建“信息不对称壁垒”,试图以此维持岗位竞争力。这种行为本质上是对安全感缺失的应激反应,但软件行业的协作模式正从“个体英雄主义”转向“模块化分工”,当项目架构趋向透明化、代码审查机制普及化时,这种隐性壁垒很容易被打破,反而会因协作效率问题加速岗位风险。

1.2 风险规避行为模式与决策延迟

在职业安全感缺失的驱动下,程序员群体形成了独特的“防御性专注”风险规避模式。这种模式的核心表现是:将精力过度集中于短期项目风险的控制,而忽视长期职业竞争力的构建。在软件项目管理中,“对比平均法”“风险矩阵评估”等工具被广泛应用,促使从业者习惯通过代码审查、单元测试覆盖率提升、线上监控告警优化等手段降低即时交付风险。例如,某互联网公司的后端团队会花费30%的工作时间优化接口响应速度从200ms至150ms,却很少讨论这种优化对个人五年后的技术竞争力有何价值。这种“短期风险聚焦”行为,本质上是将职业安全感锚定在当前项目的稳定性上,而非自身技能的迁移能力上。

不同职业阶段的程序员在风险规避行为上呈现显著差异。初级程序员(工作1-3年)更易陷入“工具焦虑”驱动的盲目学习——当市场出现新框架时,他们会优先选择“快速上手”而非“深度理解”,例如在未掌握Java并发编程核心原理的情况下,转而学习Go语言的goroutine语法,试图通过“技能数量”对冲失业风险。这种行为模式虽能缓解短期焦虑,但因缺乏知识体系整合,反而会因“样样通样样松”降低职业抗风险能力。

资深程序员(工作5年以上)则受“路径依赖”与“沉没成本效应”影响更深。他们在现有技术领域已积累大量业务经验、行业人脉和项目成果,这些资源构成了“转型成本”的核心部分。例如,一位专注于分布式系统开发的资深工程师,若考虑转行FPGA,不仅需要放弃已精通的微服务架构设计经验,还需面对薪资波动、人脉失效等现实问题。家庭责任、房贷压力等外部约束进一步放大了这种顾虑,使其更倾向于通过“在现有领域纵向深耕”而非“跨领域横向拓展”来规避风险。某技术社区调研显示,35岁以上程序员中,72%的职业规划仍聚焦于当前技术栈的深化,仅有18%考虑跨领域转型,这种决策延迟使得他们在面临行业冲击时更易陷入被动。

1.3 裁员压力下的心理转变与决策触发

裁员事件作为强烈的外部冲击,会彻底打破程序员原有的“被动稳定”心理状态,推动职业决策模式从“风险规避”转向“生存驱动”。在危机发生前,多数程序员处于“双重认知失调”状态:一方面意识到行业风险(如“35岁职场门槛”的普遍讨论),另一方面又通过“天道酬勤”“公司不会轻易裁员”等自我合理化信念维持现状。某职场社交平台的匿名调查显示,68%的程序员在裁员前3个月内曾“研究劳动法”“更新简历”,但仅有12%将计划转化为实际学习行动,这种“准备瘫痪”状态源于对“稳定假象”的心理依赖。

裁员发生后,心理防御机制会迅速启动,激发“生存本能”驱动的决策转变。典型表现为“身份焦虑”与“行动紧迫性”的叠加:当工牌被收回、企业微信被移除时,从业者会经历“职业身份剥离”的痛苦,这种痛苦会转化为强烈的行动动力。例如,某互联网公司裁员案例中,被裁员工小张在离职当天即报名FPGA线上课程,并将社交平台签名改为“一切归零,重新出发”。这种转变的核心逻辑是:裁员事件打破了“维持现状即可安全”的幻想,迫使从业者接受“职场竞争力需主动构建”的现实认知。

在决策执行阶段,“心理补偿机制”会进一步强化转型决心。部分程序员会通过“极端投入”来缓解失控感,例如拒绝薪资高于原岗位的软件开发offer,选择全职学习FPGA;或通过“社交隔离”减少外部干扰,某调研显示被裁程序员平均会删除2.7个“仅维持表面关系”的职场联系人,以降低转型过程中的心理压力。这种行为虽带有一定的应激性(如未充分评估FPGA行业真实需求),但短期内能快速建立“掌控感”,为系统性学习提供心理支撑。

值得注意的是,个体心理特质差异会导致转型路径分化。具有“固定型思维”的程序员更易将裁员归因于“自身能力不足”,在学习FPGA时过度关注“是否能达到行业标准”,遇到挫折时容易放弃;而“成长型思维”者则将裁员视为“重新选择赛道”的机会,更注重“阶段性进步”而非“完美结果”。例如,某前后端开发工程师在转行FPGA时,通过“每周完成一个小型实验项目”(如LED控制、UART通信)逐步积累信心,最终在6个月后入职芯片设计公司,这种“小步快跑”策略有效缓解了转型过程中的焦虑情绪。

二、FPGA技术门槛与转型难度评估

2.1 FPGA技术体系与程序员技能结构的差异

FPGA技术体系的核心特征是“软硬融合”,要求开发者同时掌握硬件电路原理与编程逻辑,这与多数程序员长期专注的“软件应用开发”存在显著知识断层。从底层知识结构看,FPGA开发需深入理解数字电路设计(如逻辑门、触发器、时序电路)、计算机架构(如指令流水线、Cache机制)、信号处理(如傅里叶变换、滤波器设计)等硬件相关原理,而传统软件开发的知识体系集中于操作系统接口、网络协议、业务逻辑实现等上层应用,对硬件抽象层以下的内容接触较少。例如,当软件工程师调用“printf”函数输出信息时,无需关注底层寄存器配置、时钟信号同步等细节,但FPGA开发者实现UART通信时,必须手动设计波特率发生器、校验位逻辑及时序约束,这种“从抽象到具体”的认知转换是首要障碍。

FPGA的硬件资源管理思维与软件内存管理存在本质区别。FPGA芯片包含可编程逻辑单元(LUT)、触发器(FF)、数字信号处理单元(DSP)、块RAM(BRAM)等物理资源,开发者需根据算法需求合理分配这些资源,避免因资源不足导致设计失败。例如,实现一个图像边缘检测算法时,软件工程师可直接调用OpenCV库函数,而FPGA开发者需计算卷积运算所需的LUT数量、DSP利用率及时钟频率,通过时序分析工具(如TimeQuest)优化路径延迟,确保电路在实际工作频率下稳定运行。这种“物理资源约束下的逻辑设计”思维,是软件开发者从未接触的全新领域。

时序分析是FPGA开发的核心难点,也是与软件开发差异最大的环节之一。软件程序的执行依赖CPU的指令调度,开发者无需关注代码执行的物理时间顺序;而FPGA的并行逻辑电路需严格满足时钟同步要求,任何时序违规(如建立时间不满足、保持时间冲突)都会导致电路功能异常。例如,当两个模块通过异步时钟域通信时,需设计跨时钟域处理电路(如双寄存器同步、FIFO缓冲),这种设计不仅需要掌握时序分析理论,还需通过仿真工具(如ModelSim)验证时序收敛性。某FPGA培训机构数据显示,45%的初学者项目失败源于时序问题,而这些问题在软件开发中几乎不会遇到。

2.2 硬件描述语言与软件开发思维的冲突

FPGA开发使用的硬件描述语言(HDL)如Verilog、VHDL,其设计思维与程序员熟悉的软件编程语言存在根本性差异,这种差异是转型过程中的核心认知障碍。软件编程语言(如C、Python)以“顺序执行”为核心,开发者通过“算法步骤”描述问题解决过程,例如用for循环实现数组遍历,用if-else语句处理条件分支。而HDL本质是“电路行为描述语言”,需通过代码定义硬件电路的结构与连接关系,例如Verilog中的“always @(posedge clk)”语句描述的是“当时钟上升沿到来时,触发器执行数据更新”,这种“并行逻辑+时钟驱动”的思维模式,与软件的“顺序执行+指令驱动”完全不同。

硬件描述语言中的“组合逻辑”与“时序逻辑”划分,要求开发者从“电路状态”而非“代码流程”角度思考问题。在软件编程中,变量赋值是瞬时完成的(如“a = b + c”),而在FPGA设计中,组合逻辑赋值(如assign a = b & c)会立即反映输入变化,时序逻辑赋值(如always @(posedge clk) a <= b + c)则需等待时钟触发。这种差异可能导致软件开发者写出“看似正确但实际错误”的HDL代码,例如在组合逻辑中使用非阻塞赋值(<=),或在时序逻辑中使用阻塞赋值(=),进而引发电路功能异常。某技术论坛的案例显示,60%的FPGA初学者语法错误源于未掌握赋值方式与逻辑类型的对应关系。

HDL代码的“硬件映射”特性要求开发者具备“电路可视化”能力。软件代码最终编译为机器指令,开发者无需关注CPU内部的晶体管开关状态;而HDL代码会被综合工具(如Vivado)直接转换为门级电路网表,代码风格直接影响硬件资源利用率和电路性能。例如,用C语言实现“8位计数器”时,开发者只需编写“count++”,但在Verilog中,若采用“always @(posedge clk) count <= count + 1”,综合工具会生成一个由触发器组成的时序计数器;若误写为“assign count = count + 1”,则会生成组合逻辑环,导致电路无法稳定工作。这种“代码即电路”的紧密关联,要求开发者在编写HDL时同步想象硬件结构,对软件开发者的抽象思维能力提出了全新挑战。

2.3 开发工具与实践环境的陌生化障碍

FPGA开发工具链的复杂性远超普通软件开发环境,其操作逻辑与程序员熟悉的IDE存在显著差异。主流FPGA厂商(如Xilinx、Intel)提供的开发工具(如Vivado、Quartus)集成了设计输入、逻辑综合、布局布线、时序分析、板级调试等全流程功能,但每个环节都涉及专业参数配置。例如,在Vivado中实现一个简单的LED闪烁项目,需经历“创建工程-添加约束文件-编写Verilog代码-综合(Synthesis)-实现(Implementation)-生成比特流(Generate Bitstream)-下载到开发板”等步骤,其中综合阶段需设置目标芯片型号、优化策略(面积优先/速度优先),实现阶段需配置物理约束(如引脚分配、电压标准),这些步骤对软件开发者而言完全陌生。某调研显示,零基础学习者平均需20小时才能独立完成工具链的基本操作,而掌握Visual Studio等软件IDE通常仅需2-3小时。

FPGA开发高度依赖硬件实践,开发板的额外投入与调试难度增加了转型门槛。软件编程可通过计算机独立完成,而FPGA学习必须配备专用开发板(如Xilinx Artix-7、Intel Cyclone系列),入门级开发板价格通常在500-2000元,高端型号(如支持高速接口的Kintex系列)则需数万元。硬件调试过程也更为复杂:当程序运行异常时,软件开发者可通过断点调试、日志输出快速定位问题,而FPGA开发者需使用逻辑分析仪(Logic Analyzer)或在线调试工具(如ChipScope)抓取内部信号波形,通过分析时序关系、信号状态排查故障。例如,某开发者在实现SPI通信时,软件层面可通过打印寄存器值判断数据传输是否正确,而FPGA层面需观察SCLK、MOSI信号的上升沿/下降沿是否满足时序要求,调试耗时通常是软件开发的3-5倍。

FPGA开发的“工具锁定”现象进一步增加了学习成本。不同厂商的开发工具、芯片架构存在显著差异:Xilinx的Vivado与Intel的Quartus操作逻辑不同,Lattice的FPGA资源布局与前两者也有区别,开发者若更换芯片品牌,需重新学习工具使用方法。此外,FPGA厂商会定期更新工具版本(如Vivado从2019.1升级至2023.1),每次更新可能伴随界面调整、功能增减,这种“工具迭代压力”对在职学习者而言难以承受。相比之下,软件开发者使用的VS Code、PyCharm等工具具有高度通用性,且语言标准(如C++11、Python3)相对稳定,学习成本更低。

三、学习曲线陡峭与时间成本问题

3.1 FPGA学习曲线的阶段性特征与陡峭度评估

FPGA学习曲线呈现“阶梯式上升”特征,不同阶段的知识密度与实践难度差异显著,整体陡峭度远高于软件开发。第一阶段为“基础预备期”(通常1-2个月),核心任务是掌握数字电路基础与硬件描述语言语法。学习者需从逻辑门、真值表、卡诺图等底层概念学起,理解时序电路(如触发器、寄存器)与组合电路(如多路选择器、加法器)的工作原理,同时掌握Verilog/VHDL的基本语法(如模块定义、端口声明、赋值语句)。此阶段的难点在于“硬件思维启蒙”,软件开发者常因习惯性用“变量”“函数”等软件概念理解HDL代码而陷入困境,例如将Verilog中的“reg”类型误认为“变量”,忽视其对应的触发器硬件结构。

第二阶段为“工具实践期”(通常2-3个月),重点是熟悉开发工具链与基础接口实现。学习者需掌握开发板引脚配置、时序约束编写、仿真验证方法,通过LED控制、按键消抖、UART通信等简单项目积累实践经验。此阶段的核心挑战是“理论与实践的衔接”:即使掌握了数字电路理论,在实际操作中仍可能因约束文件错误、工具参数配置不当导致项目失败。例如,某学习者在实现UART接收功能时,因未正确设置输入引脚的IO标准(如LVCMOS33),导致开发板无法识别外部信号;或因未添加时钟周期约束,综合工具生成的电路时序不满足要求,出现数据传输错误。技术社区统计显示,工具实践期的项目失败率高达65%,主要源于对硬件细节的忽视。

第三阶段为“综合项目期”(通常3-6个月),需完成中等复杂度的系统设计,标志着从“入门”到“独立开发”的跨越。典型项目包括SPI/I2C接口控制器、PWM波形发生器、图像采集与显示系统等,要求学习者综合运用数字逻辑设计、时序分析、模块划分等技能。此阶段的陡峭度达到顶峰,核心难点是“系统思维构建”:开发者需从整体角度规划模块间的信号交互、时钟域划分、资源分配,而非局限于单一功能实现。例如,在设计基于FPGA的摄像头图像采集系统时,需同时考虑图像传感器初始化(I2C通信)、数据时序同步(像素时钟与系统时钟匹配)、数据缓存(FIFO深度设计)等多维度问题,任何环节的疏漏都会导致系统功能异常。某培训机构数据显示,仅30%的学习者能独立完成综合项目,多数人因调试难度大、问题定位耗时过长而中途放弃。

3.2 从入门到独立开发的典型时间周期数据

FPGA学习的时间周期因学习路径、基础水平、投入强度的不同存在显著差异,整体呈现“有指导加速,无基础延长”的规律。培训机构的“系统化学习”模式下,时间周期相对可控。某知名FPGA培训机构的公开数据显示,零基础学员(无数字电路背景)通过全日制学习(每天8小时),平均需4.5个月达到独立开发能力,其中基础预备期1.5个月(数字电路+Verilog)、工具实践期1.5个月(开发工具+基础项目)、综合项目期1.5个月(如千兆以太网通信项目)。该机构的“精英班”学员(具备计算机专业背景)可压缩至2.5个月,通过高强度训练(每日10小时学习+项目实战)快速突破核心难点,但这类学员仅占总数的15%,且需满足“全职学习+专人辅导”条件,对在职程序员几乎不可行。

自学模式下的时间周期显著延长,且不确定性更高。技术论坛的经验分享显示,具备数字电路与C语言基础的自学者,若每天投入2-3小时,平均需6-8个月完成入门(能独立实现UART、SPI等基础接口),12-18个月达到独立开发中等复杂度项目的水平。无硬件基础的自学者则需额外3-4个月补充数字电路知识,总周期可达15-24个月。某开源社区的调研显示,自学者中途放弃率高达70%,主要原因包括:学习资源碎片化(教程质量参差不齐)、问题无人解答(调试卡壳时难以找到帮助)、缺乏项目驱动(无实际应用场景导致动力不足)。例如,一位后端开发工程师在自学FPGA时,因无法解决时序收敛问题(工具提示“setup time violation”),且网络搜索不到针对性解决方案,最终在学习4个月后放弃。

不同应用场景的FPGA开发所需时间差异显著。面向通信、工业控制等传统领域的FPGA开发,因接口协议(如Ethernet、CAN)相对成熟,学习周期较短(6-12个月);而面向AI加速、高性能计算的FPGA开发,需额外掌握算法硬件实现(如卷积神经网络加速、矩阵运算优化),学习周期延长至12-24个月。某招聘平台的岗位要求分析显示,“FPGA算法加速工程师”岗位的求职者平均需3年以上学习实践经验,远高于“FPGA接口开发工程师”的1-2年要求。这种“场景差异化”进一步增加了时间周期评估的复杂性,也使得在职程序员难以准确规划学习路径。

3.3 学习成本的多维度量化分析

FPGA学习成本需从硬件投入、时间投入、精力投入三个维度综合评估,整体量化水平显著高于软件开发。硬件投入是最直观的成本项,包括开发板、仿真工具、辅助设备等。入门级开发板(如Xilinx Spartan-7系列、Intel Cyclone IV系列)价格通常在500-1500元,适合基础学习;进阶级开发板(如Xilinx Artix-7系列、带摄像头/显示屏模块)价格1500-3000元,可支持图像采集等综合项目;高端开发板(如Xilinx Zynq系列、带ARM内核的异构平台)价格3000-10000元,用于复杂系统开发。除开发板外,部分学习者需购买逻辑分析仪(基础款2000-5000元)辅助硬件调试,若仅依赖开发板自带的LED、按键等简单外设,调试效率会大幅降低。相比之下,软件开发仅需计算机即可完成,硬件投入几乎为零。

时间投入的量化需考虑“有效学习时长”与“总周期”的乘积。按自学者平均每天2小时有效学习时间、总周期12个月计算,累计学习时长约720小时;若选择培训机构(全日制学习,每天6小时有效时间,周期4个月),累计时长约720小时,两者总时间投入相当,但在职学习需分散在1年以上,机会成本更高。某职场咨询机构的测算显示,程序员在职学习FPGA的隐性成本包括:放弃加班补贴(按日均2小时加班,时薪100元计算,12个月约6万元)、错失晋升机会(因学习占用精力导致绩效下降)、社交娱乐减少(影响心理健康)。这些隐性成本往往被忽视,但实际可能超过显性的硬件投入。

精力投入的核心是“认知转换成本”与“孤独学习成本”。从软件思维转向硬件思维需重构知识体系,这个过程伴随大量“试错-纠错”循环,认知负荷远高于同领域知识深化。例如,软件开发者学习新框架时,可基于已有编程经验快速迁移,而学习FPGA时需从零构建数字电路认知模型,每一个概念(如时序约束、跨时钟域)都需通过反复实践才能内化。此外,FPGA学习的“孤独感”显著增加精力消耗:软件领域有Stack Overflow、GitHub等丰富社区资源,问题响应时间通常在1小时内;而FPGA社区规模较小(如国内FPGA论坛日均发帖量不足软件开发论坛的1/10),硬件问题因环境依赖性强(如特定开发板型号、工具版本),往往难以通过网络提问解决。某自学者反馈,曾因一个引脚约束错误卡壳两周,最终通过付费咨询才得以解决,这种“求助无门”的经历会持续消耗学习动力。

四、在职学习的技术与时间冲突

4.1 在职程序员的时间分配现状与学习可行性

在职程序员的时间分配呈现“高强度工作挤压学习时间”的特征,可用于FPGA学习的有效时长严重不足,系统性学习可行性较低。行业调研显示,国内互联网、软件企业的程序员日均有效工作时长普遍超过10小时,其中包含2-3小时加班(主动或被动)、1-2小时通勤时间,剩余可支配时间(扣除睡眠7-8小时、餐饮1-2小时)通常仅3-4小时。这些时间需优先满足家庭责任(如照顾子女、家务劳动)、生理恢复(如运动、休息)等基本需求,实际可用于学习的时间被进一步压缩至1-2小时/天,且呈现“碎片化”分布(如通勤时刷教程、午休时看文档)。

碎片化学习模式与FPGA的系统性学习需求存在根本矛盾。FPGA学习强调“理论-实践-反馈”的闭环,需连续3-4小时的专注时间完成“代码编写-仿真验证-硬件调试”全流程,而碎片化时间(如15分钟通勤)仅能满足知识点记忆(如Verilog语法),无法支撑深度思考与实践操作。某技术社区的在职学习案例显示,一位后端工程师尝试利用通勤时间学习FPGA,3个月内累计观看了50小时教程视频,能背诵Verilog语法规则,但在首次实践LED控制项目时,因无法理解约束文件编写逻辑、工具操作流程,最终耗时2周才完成(相当于全职学习1天的工作量)。这种“高投入低产出”现象普遍存在,65%的在职学习者承认“碎片化学习效率低下”,仅32%能保证每周10小时以上的系统性学习(连续3小时以上的专注时段)。

项目紧急迭代期的“时间黑洞”进一步冲击学习计划。软件行业的“敏捷开发”“快速迭代”模式导致工作节奏极不稳定,当项目进入上线冲刺阶段(如“双11”“618”前),程序员常面临连续数周的“996”甚至“007”工作模式,此时学习计划被迫中断。某电商平台的程序员反馈,其年度学习计划因项目迭代被打断3-4次,每次中断后需1-2周重新找回学习状态,全年有效学习时间不足计划的50%。FPGA学习的“连续性要求”(如时序分析、项目调试需连贯思维)使得这种中断的影响尤为严重,部分学习者因多次中断最终放弃。

4.2 工作压力对学习效率的抑制效应

长期高强度工作压力会从生理与心理层面双重抑制FPGA学习效率,形成“高压工作-疲劳-低效学习-更焦虑”的恶性循环。生理层面,持续工作压力会导致皮质醇水平升高,抑制大脑前额叶皮层的神经活动——该区域负责逻辑推理、问题解决等高级认知功能,而FPGA学习恰好高度依赖这些能力。心理学研究表明,当工作时长超过8小时后,每增加1小时工作时间,前额叶皮层活跃度下降15%-20%,导致学习新技能时的注意力集中时间缩短、错误率上升。例如,一位经历12小时工作的程序员,在学习时序约束概念时,可能需要反复阅读3-4遍才能理解,而在休息充分状态下仅需1遍。

心理层面,工作压力会引发“资源耗竭”效应,降低学习动力与抗挫折能力。软件项目中的线上故障处理、需求频繁变更、跨团队协作冲突等问题,会消耗大量心理资源(如情绪调节、意志力),导致下班后进入“心理疲劳”状态。此时,程序员更倾向选择“低认知负荷”活动(如刷短视频、玩游戏)进行放松,而非启动“高认知负荷”的FPGA学习。某职场心理健康调研显示,83%的程序员下班后“不想再接触任何代码相关内容”,这种“心理排斥”使得学习计划难以执行。即使勉强开始学习,也会因精力不足导致效率低下,例如在编写TestBench仿真文件时,因注意力不集中出现语法错误,或在分析仿真波形时遗漏关键信号状态,进而产生“学习困难”的挫败感,加剧焦虑情绪。

工作压力还会通过“认知固化”效应阻碍硬件思维的建立。程序员在长期软件开发中形成了“指令执行”“变量操作”的思维定式,这种定式在工作中是高效的,但在FPGA学习中会成为障碍。当工作压力大时,大脑为节省认知资源,会更依赖“自动化思维模式”,难以切换到“硬件电路思维”。例如,在编写Verilog代码时,软件开发者会习惯性地用“for循环”实现重复操作,忽视FPGA的并行逻辑特性,写出综合效率低下的代码;或在调试时,试图通过“打印变量值”定位问题,而非分析信号时序关系。这种“思维切换困难”导致学习效率进一步降低,形成恶性循环。

4.3 在职学习FPGA的技术障碍与实践困境

在职学习FPGA面临“基础知识断层”与“实践机会缺乏”的双重技术障碍,导致学习过程举步维艰。基础知识断层主要体现在硬件背景缺失:多数程序员缺乏数字电路、计算机组成原理等底层知识,在学习FPGA时需“边学边补”,大幅增加学习负担。例如,理解时序约束需先掌握时钟周期、建立时间、保持时间等概念,而这些内容在软件开发课程中通常不涉及;实现PWM波形发生器需理解计数器、比较器的硬件结构,软件开发者需额外学习数字电路设计原理。某在线教育平台的课程数据显示,无硬件背景的在职学习者,需用30%的学习时间补充基础知识,远高于计算机专业出身的学习者(10%)。

实践机会缺乏是在职学习的核心技术困境,表现为“无真实项目驱动”与“调试环境不足”。软件开发者可通过个人项目(如开发网站、APP)积累经验,而FPGA开发需硬件开发板支持,且缺乏真实应用场景会导致“纸上谈兵”。例如,一位自学FPGA的前端工程师,在完成UART通信理论学习后,因无传感器、显示屏等外设,无法验证代码在实际硬件中的运行效果,只能通过仿真波形判断功能正确性,这种“脱离实际”的学习使得知识难以内化。部分学习者尝试购买开发板,但因缺乏项目需求(如“做什么项目”“解决什么问题”),常陷入“不知道学了有什么用”的迷茫,学习动力逐渐下降。

企业环境限制进一步加剧实践困境。多数互联网、软件公司的工作环境以纯软件开发为主,程序员难以接触到FPGA相关项目,无法在工作中积累硬件开发经验。即使部分公司有硬件团队,软件与硬件部门通常存在协作壁垒,软件工程师很少有机会参与FPGA开发流程。某芯片设计公司的调研显示,跨部门参与FPGA项目的软件工程师不足5%,且多为“算法移植”等边缘工作,无法深入核心设计。这种“工作环境与学习目标脱节”的状况,使得在职学习者只能依赖业余时间进行“模拟项目”练习,与真实工业场景存在差距,转型后仍需重新适应企业级开发流程。

五、行业认知偏差与信息不对称

5.1 FPGA行业前景与应用场景的认知误区

程序员对FPGA行业前景与应用场景存在显著认知误区,这些误区源于信息片面性与刻板印象,降低了主动学习的意愿。最普遍的误区是“FPGA应用场景局限于通信、军工等传统领域”,忽视其在新兴技术中的广泛需求。事实上,FPGA凭借并行计算、低延迟、高能效比等优势,已成为AI加速、边缘计算、智能汽车等领域的核心硬件平台。例如,在AI边缘端部署中,FPGA可实现深度学习模型的实时推理(如人脸识别响应时间<10ms),能效比是CPU的10-20倍;在智能汽车领域,FPGA用于激光雷达信号处理、自动驾驶算法加速,某新能源车企的自动驾驶域控制器中集成了4颗FPGA芯片,负责传感器数据融合与实时决策。行业报告显示,2024年全球FPGA市场规模已突破150亿美元,其中新兴领域(AI、汽车、工业互联网)贡献了60%的增长,远高于传统通信领域的25%。

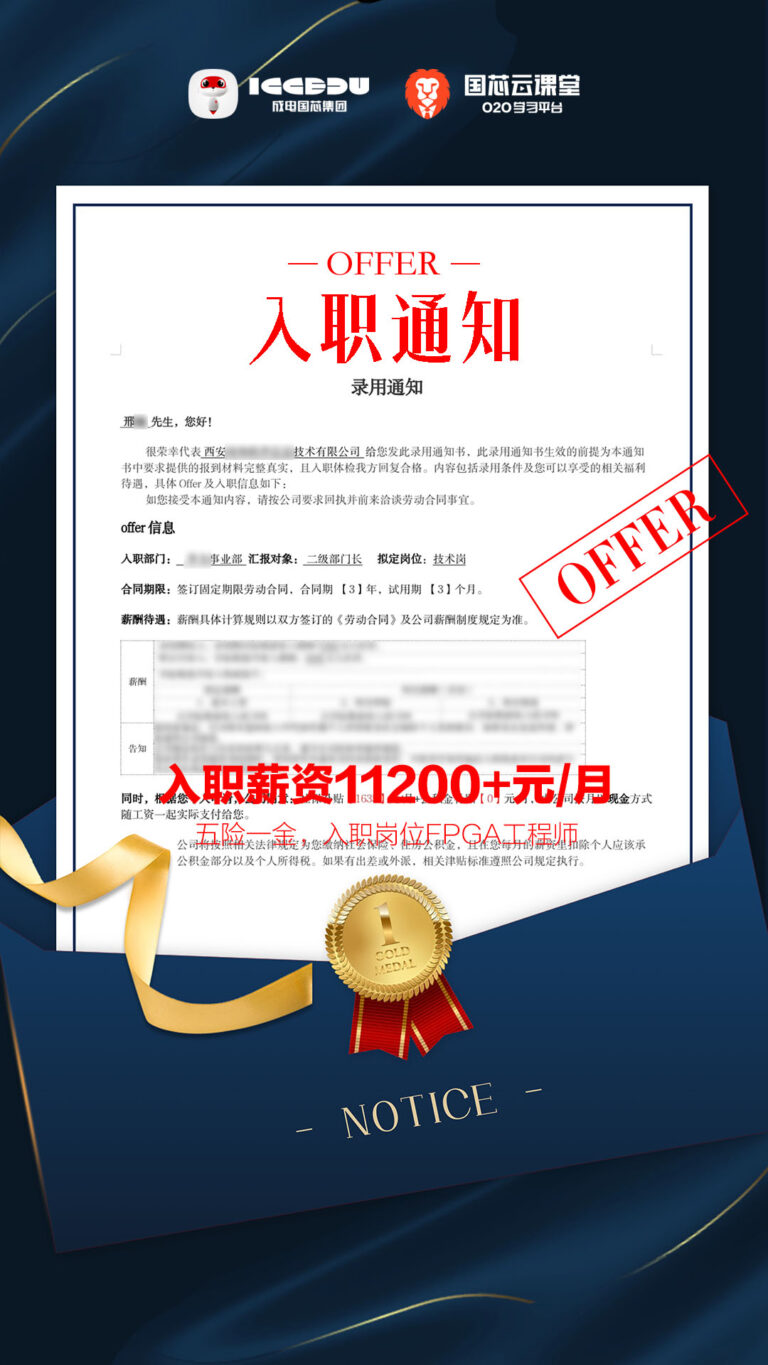

“FPGA薪资与软件差距不大”的认知误区也普遍存在,导致程序员低估转型收益。实际数据显示,FPGA工程师的薪资水平显著高于同经验软件开发工程师。招聘平台统计显示,国内FPGA应届生起薪普遍为15-25万元/年,3年经验者可达30-50万元/年,5年以上资深工程师年薪轻松突破60万元,技术专家级人才(如AI加速方向)年薪可达百万级;而同期软件开发工程师的应届生起薪为12-20万元/年,3年经验者25-40万元/年,薪资差距随经验增长逐渐扩大。这种差距源于FPGA人才供需失衡:2024年国内FPGA工程师缺口超30万人,而高校相关专业毕业生仅1万人/年,企业为争夺人才不得不提高薪资。某芯片设计公司的招聘负责人表示,“3年经验的FPGA工程师,跳槽薪资涨幅通常在30%-50%,远高于软件工程师的20%-30%”。

“FPGA学习难度过高,性价比低”的认知进一步抑制学习动力。部分程序员因听说“FPGA需要硬件背景”“学习周期长”,便主观判定“转型成本高于收益”。这种认知忽视了“软件转FPGA的独特优势”:具备算法实现经验的程序员,在FPGA算法加速(如AI模型部署、信号处理)领域反而更具竞争力。例如,一位熟悉深度学习框架的软件工程师,在掌握FPGA基础后,可快速理解“卷积层硬件实现”“权值量化”等核心技术,转型为AI加速工程师,这类复合型人才薪资溢价显著(比纯硬件背景高20%-30%)。某培训机构数据显示,软件背景的FPGA学习者中,65%最终进入AI加速、边缘计算等高薪领域,平均转型周期10-12个月,投资回报率(薪资涨幅/学习时间)高于同周期软件领域深耕。

5.2 招聘信息与技能要求的信息不对称

FPGA岗位招聘信息中的“专业术语壁垒”与“技能要求模糊性”,导致程序员对转型难度产生高估,形成信息不对称下的决策障碍。招聘描述中频繁出现的“时序收敛”“逻辑综合”“硬核IP集成”等专业术语,对缺乏硬件背景的程序员而言如同“天书”,使其错误认为“必须掌握所有技能才能应聘”。实际上,企业对不同层级FPGA岗位的要求存在显著差异:初级岗位(如FPGA开发工程师)更关注“逻辑设计能力”(如Verilog编码、基础接口实现),对“时序分析深度”“硬件架构设计”要求较低;资深岗位(如FPGA技术专家)才强调“系统级设计”“性能优化”等高级技能。例如,某智能网卡公司的FPGA开发工程师岗位要求“完成算法的FPGA转换,实现数据采集传输处理”,实际工作中会有算法工程师提供详细流程,开发者只需掌握Verilog语法、基础时序约束即可胜任,无需深入理解底层硬件架构。

招聘信息中的“经验要求”常被误解为“必须有相关工作经验”,忽视“项目经验”的替代价值。多数FPGA岗位要求“1-3年FPGA开发经验”,但企业更看重“实际项目能力”而非“工作经历”。自学过程中完成的综合项目(如基于FPGA的图像识别系统、高速接口控制器),若能提供完整代码、仿真报告、硬件调试记录,可作为“项目经验”证明能力,部分企业甚至认可开源社区贡献(如GitHub上的FPGA项目)。某半导体公司的HR表示,“我们招聘过一位前Java开发工程师,他虽然没有FPGA工作经验,但独立完成了基于FPGA的RISC-V处理器实现,代码质量和文档完整性远超应届生,最终顺利入职”。这种“项目经验替代工作经验”的可能性,因招聘信息未明确说明而被多数程序员忽视。

不同行业的FPGA岗位技能要求差异被低估,导致程序员难以找到“适配自身背景的切入点”。FPGA应用领域广泛,通信、工业控制、AI加速、汽车电子等行业的技能要求各不相同:通信领域强调“高速接口(如SerDes、PCIe)”“协议处理(如TCP/IP、5G)”;工业控制领域侧重“实时性”“可靠性设计”;AI加速领域则关注“算法硬件映射”“性能优化”。软件背景的程序员可根据自身优势选择切入点:例如,有嵌入式开发经验者可优先考虑工业控制方向(熟悉单片机接口,转型难度低);有AI算法经验者可聚焦AI加速方向(算法理解能力强,硬件实现可逐步学习)。但招聘信息通常未明确行业差异,统一标注“熟悉FPGA开发流程”,使得程序员难以判断“自己适合哪个方向”,进而放弃尝试。

5.3 行业交流壁垒与认知更新滞后

FPGA行业的“小众性”与“技术封闭性”导致行业交流壁垒较高,程序员难以获取准确认知,形成“信息茧房”下的认知滞后。FPGA社区规模远小于软件开发社区:国内最大的FPGA论坛注册用户约50万人,而Java论坛超过500万人;GitHub上FPGA相关开源项目不足10万,仅为Python项目的1/20。社区资源匮乏使得学习过程中遇到的问题难以快速解决,例如调试时出现“metastability”(亚稳态)问题,软件社区几乎无相关讨论,需查阅厂商手册或付费咨询专家,这种“求助无门”的体验会强化“FPGA学习难”的认知。

FPGA厂商的技术文档与工具链存在“封闭性”,进一步加剧信息不对称。Xilinx、Intel等主流厂商的官方文档(如UG系列用户指南)虽详尽,但内容侧重“工具操作”而非“原理讲解”,且充斥大量厂商特定术语(如Xilinx的“UltraRAM”、Intel的“M20K”),初学者难以理解其本质。开发工具(如Vivado)的“黑箱化”设计也隐藏了关键细节:综合工具如何将HDL代码转换为电路网表、布局布线算法如何优化时序,这些信息对理解FPGA工作原理至关重要,但厂商未公开,导致学习者只能“知其然不知其所以然”。相比之下,软件领域的编译器原理、操作系统源码完全开源,社区有大量“底层原理剖析”资源,学习透明度高。

技术迭代速度与信息传播效率的不匹配,导致程序员对FPGA行业趋势认知滞后。FPGA技术正从“硬件逻辑实现”向“软硬协同设计”转型(如Xilinx Zynq、Intel Agilex系列的异构架构),要求开发者同时掌握FPGA逻辑设计与嵌入式软件开发(如ARM编程)。这种趋势对软件背景的程序员而言是利好——他们可发挥“软硬协同”优势,但多数程序员仍停留在“FPGA=纯硬件开发”的旧认知,未意识到转型机会。某行业报告显示,60%的FPGA岗位已要求“熟悉嵌入式Linux”“具备C/C++编程能力”,这些正是软件工程师的强项,但因信息传播滞后,仅25%的软件开发者了解这一变化。

行业交流壁垒还体现在“人脉资源匮乏”。程序员的社交圈多局限于软件领域,缺乏FPGA从业者的交流渠道,难以获取“一手信息”(如企业真实技能需求、转型经验)。某职场社交平台的调研显示,80%的软件工程师“身边没有FPGA工程师朋友”,75%的FPGA行业认知来自“网络文章”或“培训机构宣传”,这些信息可能存在片面性或夸大成分。例如,部分文章过度强调“FPGA高门槛”,却未提及“软件转FPGA的成功案例”;培训机构则可能夸大“就业薪资”,忽视转型风险。这种“间接信息依赖”使得程序员难以形成客观认知,最终选择“维持现状”而非“主动探索”。