2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

成电国芯如何带领0基础小白入门FPGA:从需求分析到上板调试的全流程指南

成电国芯如何带领0基础小白入门FPGA:从需求分析到上板调试的全流程指南

成电国芯针对零基础学员设计了一套系统化的FPGA入门培养方案,以“需求分析-原理讲解-代码实操-仿真验证-上板调试”为核心流程,结合企业级项目实战,帮助学员从理论到工程能力全面突破。以下是具体流程及案例解析:

一、零基础入门FPGA标准流程

1. 需求分析:从企业真实场景拆解目标

行业需求调研:结合华为、中兴等合作企业的FPGA岗位需求,明确核心技能(如Verilog编程、时序约束、高速接口设计)。

项目目标拆解:将复杂项目(如通信模块、图像处理)拆解为可执行的子任务,例如“智能循迹小车”需实现传感器数据采集、电机控制、路径决策等模块。

学习路径规划:根据学员基础定制阶段性目标,例如零基础学员先掌握“数字电路基础→Verilog语法→工具链操作”,再进阶到项目开发。

2. 原理讲解:用生活化比喻降低抽象门槛

硬件原理可视化:

- 用“食堂叫号器”比喻时钟信号(时钟沿触发数据更新),用“快递分拣中心”类比FPGA内部逻辑单元(CLB)的并行处理能力。

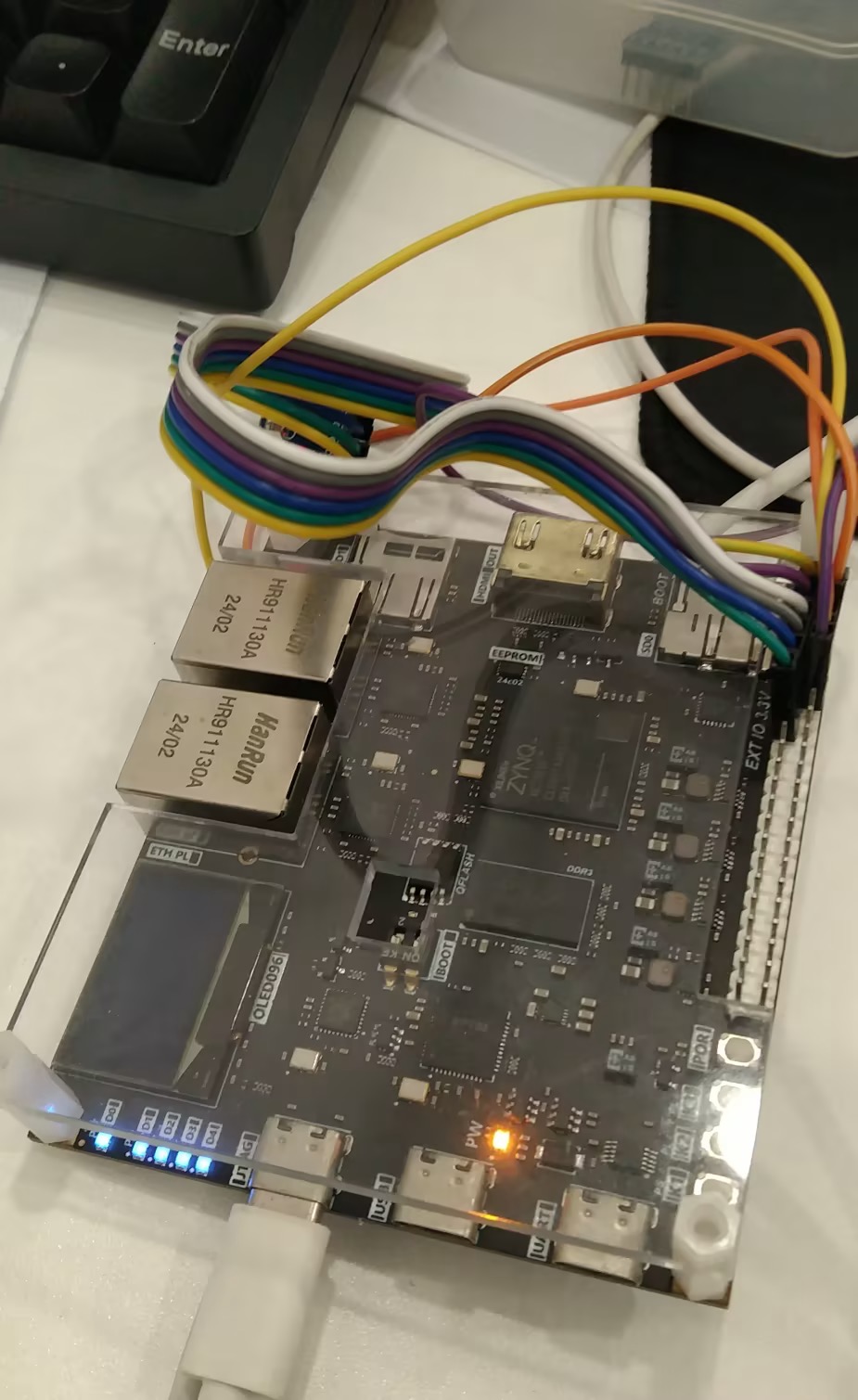

- 通过动画演示FPGA架构(查找表LUT、触发器、布线资源),结合Xilinx Artix-7开发板实物图,直观理解“可编程逻辑”的本质。

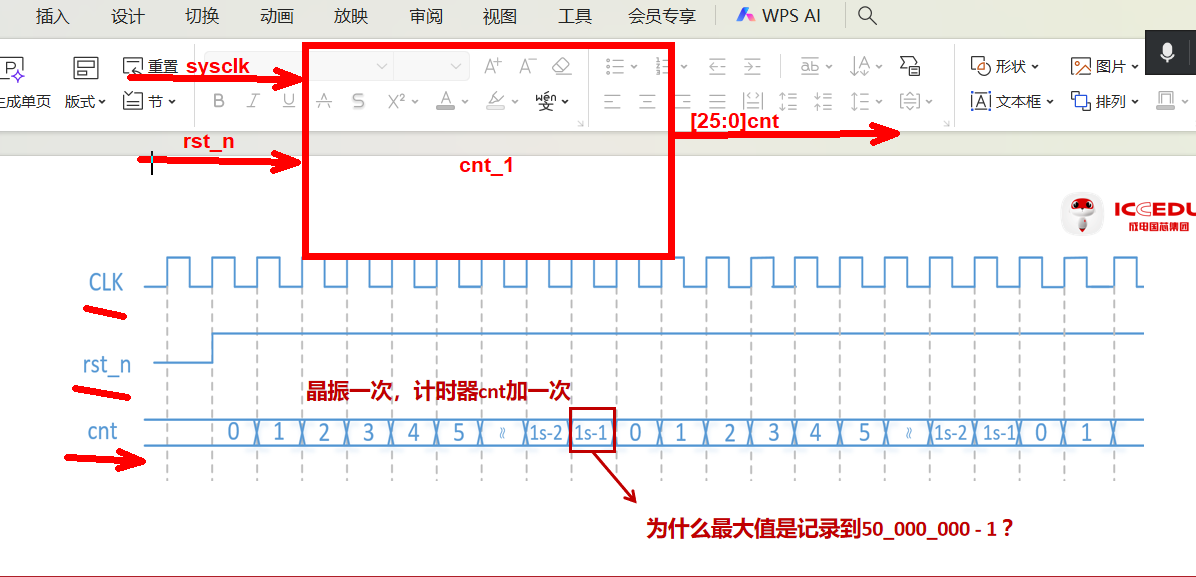

数字电路核心概念:

- 组合逻辑(如多路选择器):用“交通信号灯切换”案例讲解输入输出实时映射关系;

- 时序逻辑(如计数器):结合“秒表计时”说明时钟同步与状态保持机制。

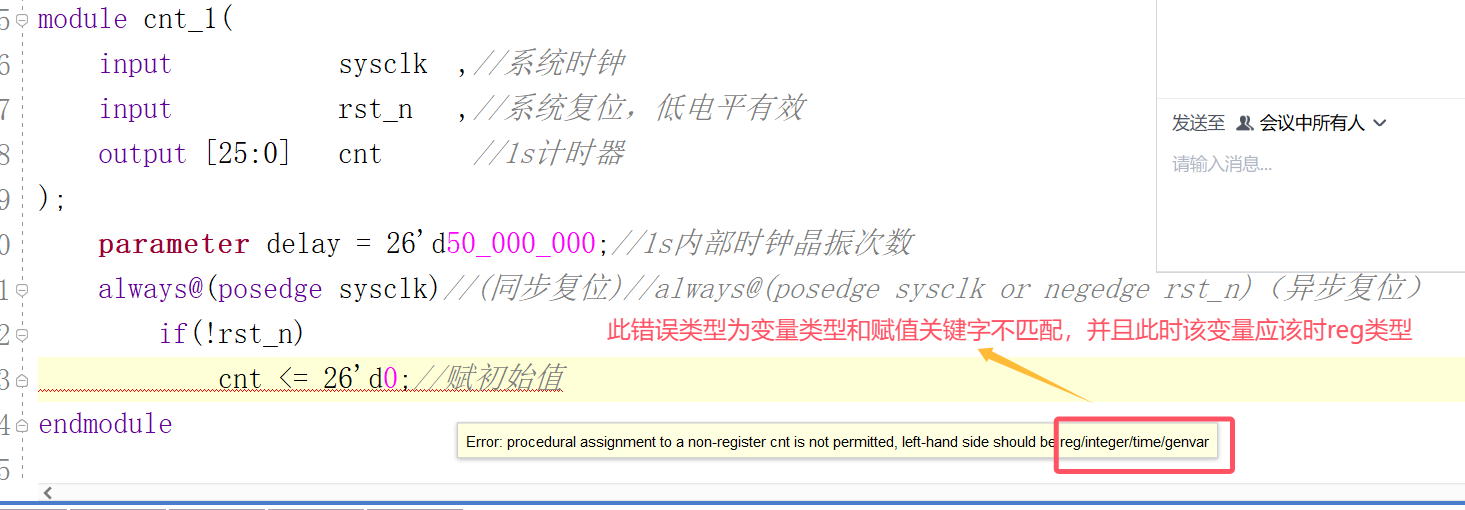

3. 代码讲解与注释:从“语法规则”到“硬件映射”

Verilog教学三步法:

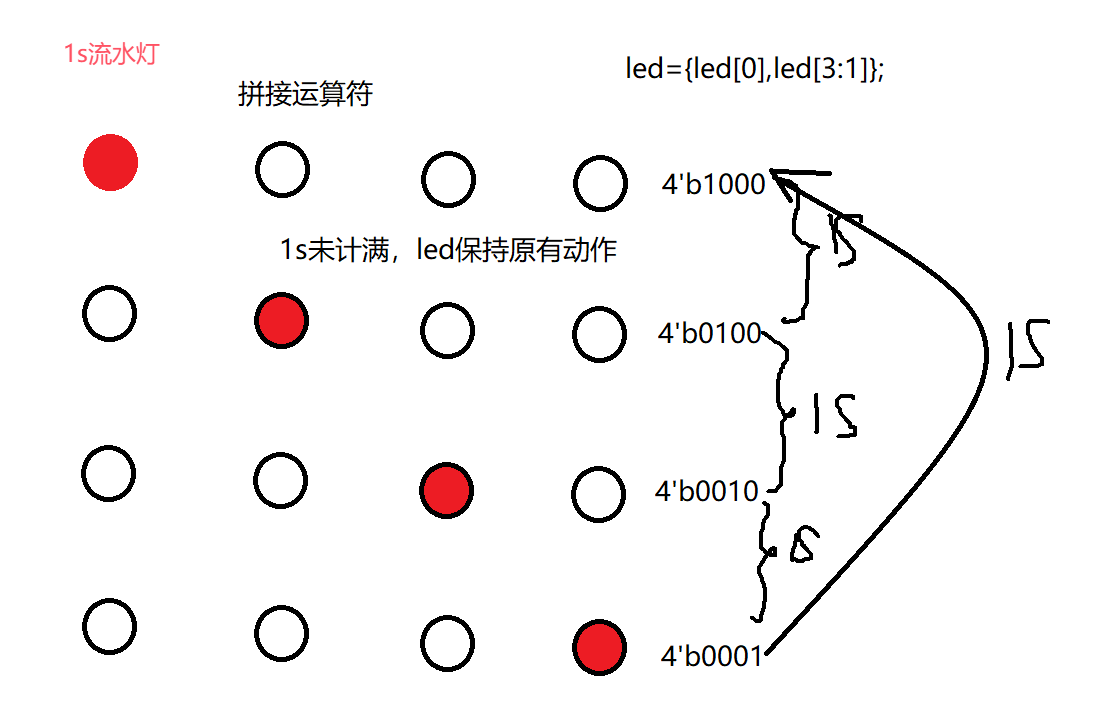

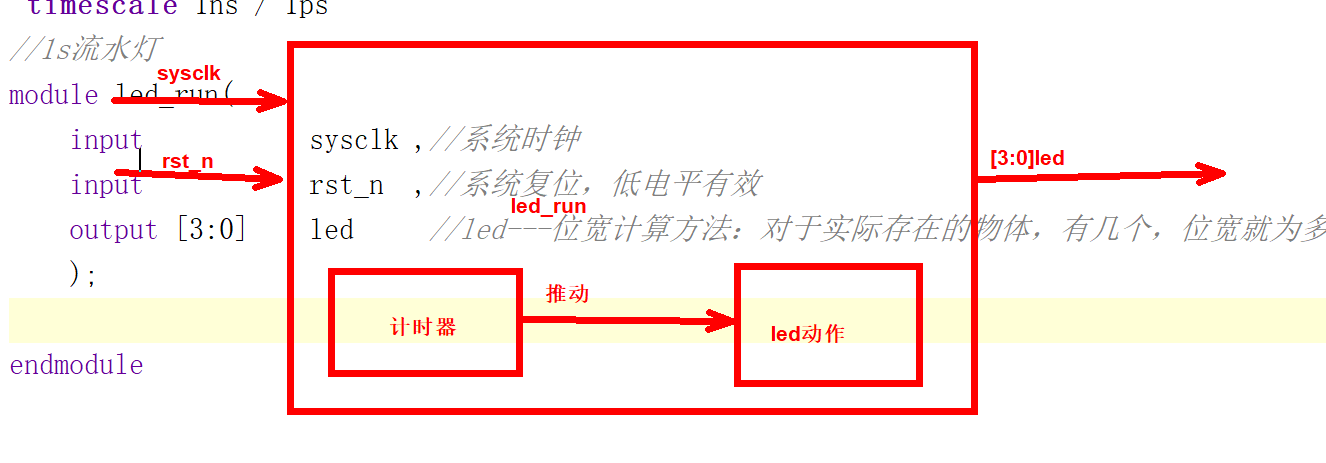

- 语法基础:通过“与非门设计”讲解

module定义、assign连续赋值,强调“硬件并行性”与软件的区别(如避免for循环滥用); - 模块实战:以“LED流水灯”为例,逐行注释代码功能:

module led_flow(

input clk, // 系统时钟(50MHz)

input rst_n, // 复位信号(低电平有效)

output reg [3:0] led // 4位LED输出

);

reg [23:0] cnt; // 计数器,用于分频(50MHz→2Hz)

always @(posedge clk or negedge rst_n) begin

if(!rst_n) cnt <= 0; // 复位时计数器清零

else cnt <= cnt + 1; // 时钟上升沿计数

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) led <= 4'b0001; // 初始状态:第一个LED亮

else if(cnt == 24'd25_000_000) begin // 0.5秒切换一次

led <= {led[2:0], led[3]}; // 左移操作,实现流水效果

end

end

endmodule- 错误案例分析:展示“忘记复位信号导致上电状态不确定”“阻塞赋值(=)与非阻塞赋值(<=)混用引发时序错误”等常见问题,配合波形图对比正确与错误结果。

4. 仿真验证:用ModelSim构建“虚拟实验室”

Testbench编写:

为“LED流水灯”编写仿真激励,模拟时钟、复位信号,并监测LED输出:

module tb_led_flow;

reg clk;

reg rst_n;

wire [3:0] led;

led_flow uut(.clk(clk), .rst_n(rst_n), .led(led));

initial begin

clk = 0; forever #10 clk = ~clk; // 生成50MHz时钟(周期20ns)

end

initial begin

rst_n = 0; #200 rst_n = 1; // 复位200ns后释放

#1000000 $finish; // 仿真1ms后结束

end

endmodule波形图分析:

通过ModelSim观察cnt计数器变化与led状态切换的对应关系,验证“每0.5秒左移一次”的逻辑是否正确,重点标注时钟沿与数据更新的时序关系。

5. 上板调试:从“虚拟仿真”到“硬件落地”

开发工具链操作:

使用Vivado完成“工程创建→综合(Synthesis)→实现(Implementation)→生成比特流(Bitstream)”全流程,讲解“时序约束”(如设置输入输出延迟)对硬件稳定性的影响。

板级调试技巧:

- 用ILA(集成逻辑分析仪)抓取实时信号,定位“按键消抖不彻底”“电机驱动信号延迟”等硬件问题;

- 结合Xilinx ECO开发板的LED、按键等外设,通过“分模块测试→联调”逐步验证系统功能。

二、实战案例:智能循迹小车项目全流程

1. 需求分析

- 功能目标:小车通过红外传感器识别黑色轨迹,自动纠正方向并保持前进,实现速度闭环控制。

- 技术拆解:传感器数据采集(ADC接口)、PID算法实现(Verilog状态机)、电机驱动(PWM模块)。

2. 原理讲解

- 传感器原理:红外对管“发射-接收”强度与距离的关系,用“手电筒照射不同颜色物体的反射差异”类比;

- PID控制:以“驾驶汽车修正方向”比喻比例(P)、积分(I)、微分(D)的作用,结合公式推导参数整定逻辑。

3. 代码实现

- 核心模块示例(PID控制器):

module pid_controller(

input clk,

input rst_n,

input [11:0] error, // 轨迹偏差(传感器差值)

output reg [9:0] pwm_out // 电机PWM占空比

);

reg [11:0] integral, derivative;

reg [11:0] error_prev; // 上一周期偏差

parameter Kp=5, Ki=1, Kd=2; // 控制参数

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

integral <= 0;

derivative <= 0;

error_prev <= 0;

end else begin

integral <= integral + error; // 积分项累加

derivative <= error - error_prev; // 微分项=当前偏差-上一偏差

error_prev <= error;

pwm_out <= Kp*error + Ki*integral + Kd*derivative; // PID输出

end

end

endmodule4. 仿真验证

- 仿真场景:模拟传感器检测到轨迹左偏、右偏、居中三种情况,观察PWM输出是否按预期调整(如左偏时右侧电机PWM增大,纠正方向)。

5. 上板调试

- 硬件连接:将传感器模块、电机驱动板与FPGA开发板通过GPIO接口连接,使用杜邦线按电路原理图接线;

- 问题排查:若小车偏离轨迹,通过ILA抓取

error信号波形,发现传感器采样延迟,需在代码中加入数据缓存模块优化。

三、学习支持体系

- 工具与资源:提供Xilinx Vivado软件安装包、开发板(如Zynq-7000)、企业级项目源码(含注释);

- 辅导机制:1V1线上答疑(2小时内响应)、每周直播复盘(针对共性问题讲解);

- 考核认证:完成项目后颁发FPGA初级工程师证书,优秀学员可内推至合作企业。

通过以上流程,成电国芯将抽象的FPGA技术转化为“可拆解、可验证、可落地”的工程能力,零基础学员可在4-6个月内掌握从需求分析到上板调试的全流程开发技能。