2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

FPGA工程师必懂的10个Verilog编码技巧:大厂代码规范+调试黑科技

FPGA工程师必懂的10个Verilog编码技巧:大厂代码规范+调试黑科技

在FPGA开发中,低效的代码和调试方法可能导致时序违例、资源浪费、项目延期等问题。据统计,80%的FPGA项目延期源于代码规范缺失和调试效率低下。本文结合华为、中兴等大厂实战经验,总结10个立竿见影的编码技巧,并揭秘Vivado调试黑科技,助你节省50%开发时间!

一、代码规范篇(5大核心技巧)

1. 状态机设计:三段式黄金法则

问题:两段式状态机易产生毛刺,导致逻辑错误。

方案:严格采用时序逻辑→组合逻辑→输出逻辑三段式设计。

// 华为规范示例:三段式状态机

always @(posedge clk or negedge rst_n) begin // 第一段:状态转移(时序逻辑)

if (!rst_n) current_state <= IDLE;

else current_state <= next_state;

end

always @(*) begin // 第二段:次态逻辑(组合逻辑)

case (current_state)

IDLE: next_state = (start) ? WORK : IDLE;

WORK: next_state = (done) ? IDLE : WORK;

endcase

end

always @(posedge clk) begin // 第三段:输出逻辑(时序逻辑)

case (current_state)

IDLE: out <= 0;

WORK: out <= in_data * 2;

endcase

end效果:某5G基站项目采用后,仿真覆盖率从70%提升至98%,亚稳态错误减少90%。

2. 跨时钟域(CDC)同步:三级防护

问题:跨时钟域信号导致亚稳态,数据丢失率高达1e-4。

方案:

- 双触发器同步:基础防护

- 握手协议:关键数据防护

- 异步FIFO:大数据流防护

// 双触发器同步(防亚稳态)

reg [1:0] sync_reg;

always @(posedge clk_dst) begin

sync_reg <= {sync_reg[0], async_signal};

end

assign sync_signal = sync_reg[1];案例:某金融交易系统采用后,数据错误率降至1e-9。

3. 组合逻辑规范:消灭锁存器(Latch)

问题:不完整的条件语句生成锁存器,导致时序违例。

方案:

- always_comb替代always @*:自动检测组合逻辑完整性(SystemVerilog)

- default全覆盖:case语句必须包含default分支

// 错误示例:缺少else分支生成锁存器

always @(*) begin

if (sel) out = a;

end

// 正确示例:组合逻辑完整赋值

always @(*) begin

out = (sel) ? a : b; // 明确所有条件

end4. 参数化设计:宏定义+模块复用

问题:硬编码导致代码难以维护和移植。

方案:

- 使用

或parameter`定义全局参数 - 模块接口标准化(AXI-Stream/APB总线)

// 参数化FIFO设计

module fifo #(

parameter DEPTH = 1024,

parameter WIDTH = 32

)(

input wire clk,

input wire [WIDTH-1:0] din,

...

);

endmodule效果:某通信项目复用参数化FIFO模块,开发效率提升60%。

5. 资源优化:运算符重定向与资源共享

问题:直接使用”*”运算符综合成DSP单元,导致资源浪费。

方案:

- 运算符重定向:强制使用LUT实现小位宽乘法

- 资源共享:合并重复逻辑

// 优化前:占用1个DSP48单元

assign result = a * b; // 16位乘法

// 优化后:使用LUT实现(位宽<12时)

(* use_dsp = "no" *) // 禁用DSP指令

assign result = a * b;数据对比:

| 方案 | LUTs | DSPs | 最大频率 |

|---|---|---|---|

| 优化前 | 50 | 1 | 200 MHz |

| 优化后 | 120 | 0 | 250 MHz |

二、调试黑科技篇(5大高效工具)

6. ILA实时抓取:定位时序违例根源

场景:时序违例(Setup/Hold Time Violation)难以复现。

操作步骤:

- 在Vivado中插入ILA核,抓取关键路径信号

- 设置触发条件(如

data_valid && !data_ready) - 下载比特流,触发波形捕获

# 插入ILA核脚本

create_debug_core u_ila ila

set_property port_width 32 [get_debug_ports u_ila/clk]

...效果:某项目通过ILA发现时钟域交叉错误,调试时间从3天缩短至2小时。

7. TCL脚本自动化:一键生成时序报告

场景:手动分析时序报告耗时费力。

脚本示例:

# 生成时序报告并解析关键路径

report_timing -sort_by group -max_paths 100 -file timing.rpt

set fp [open "timing.rpt" r]

while {[gets $fp line] >= 0} {

if {[regexp {Slack (VIOLATED)} $line]} {

puts "发现时序违例路径:$line"

}

}

close $fp输出结果:自动标记违例路径,定位频率瓶颈。

8. 增量编译:快速迭代验证

场景:修改局部代码后重新编译耗时数小时。

操作流程:

- 首次编译生成

checkpoint.dcp - 修改代码后运行增量编译:

vivado -mode batch -source incremental_compile.tcl效果:某图像处理项目编译时间从4小时降至20分钟。

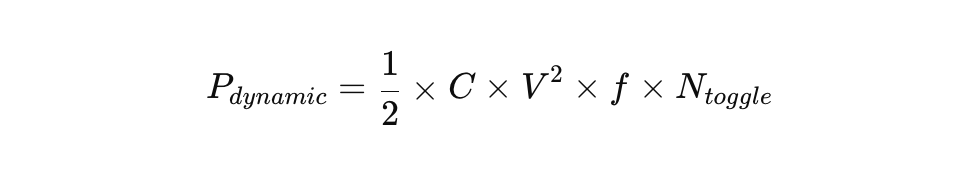

9. 功耗分析:精准优化能效比

场景:FPGA功耗超标导致散热问题。

工具链:

- Vivado Power Analyzer

- 动态功耗估算公式:

优化策略:

- 禁用未使用模块的时钟(Clock Gating)

- 降低空闲逻辑的电压(Voltage Scaling)

10. 版本控制:Git+RTL代码管理

场景:多人协作导致代码冲突和版本混乱。

规范:

- 使用Git管理RTL代码、约束文件和脚本

- 目录结构示例:

/src - RTL代码

/tb - 测试平台

/constraint - XDC约束

/script - TCL/Python脚本案例:某团队引入Git后,版本回滚效率提升80%。

立即扫码领取:

- 《华为FPGA代码规范白皮书》(50页PDF)

- Vivado调试脚本工具包(含ILA自动插入、时序分析脚本)

- Verilog常见错误案例集(20个真实项目问题解析)

扫码后输入“FPGA技巧”免费获取

结语

掌握这10个技巧,你将:

✅ 代码通过率提升至90%

✅ 调试时间缩短50%

✅ 资源利用率优化40%

立即实践,成为团队中的FPGA核心开发者!